# Hardware Bugs and Fuzzing

**Mengjia Yan** Spring 2025

sysret slides credit: Will Liu (MIT)

#### What is Errata?

#### 8<sup>th</sup> and 9<sup>th</sup> Generation Intel<sup>®</sup> Core<sup>™</sup> Processor Family

**Specification Update**

Supporting 8<sup>th</sup> Generation Intel<sup>®</sup> Core<sup>™</sup> Processor Families for S/H/U Platforms, formerly known as Coffee Lake

Supporting 9<sup>th</sup> Generation Intel® Core™ Processor Families Processors for S/H Platforms, formerly known as Coffee Lake Refresh

November 2019

**Revision 002**

It is a compilation of device and document errata and specification clarifications and changes, which is intended for hardware system manufacturers and for software developers of applications, operating system, and tools.

**Errata** are design defects or errors. Errata may cause the processor's behavior to deviate from published specifications. Hardware and software designed to be used with any given stepping must assume that all errata documented for that stepping are present on all devices.

#### **Errata Table Example**

#### 3.2 **Errata Summary Information Table 4-3. Errata Summary Table Processor Line / Stepping** S н U ID Title **Reported Memory Type May Not Be Used to Access the VMCS and** 001 **Referenced Data Structures** 00: Bits 53:50 of the IA32\_VMX\_BASIC MSR report the memory type that the processor uses to access the VMCS and data structures referenced by pointers in the VMCS. Problem Due to this erratum, a VMX access to the VMCS or referenced data structures will 002 instead use the memory type that the memory-type range registers (MTRRs) specify for the physical address of the access. 003 Bits 53:50 of the IA32\_VMX\_BASIC MSR report that the write-back (WB) memory Implication type will be used, but the processor may use a different memory type. 004 Software should ensure that the VMCS and referenced data structures are located at Workaround physical addresses that are mapped to WB memory type by the MTRRs. Status For the steppings affected, refer the Summary Table of Changes.

#### **More Errata**

####

| Revision G | uide  | for |

|------------|-------|-----|

| AMD Fam    | ily 1 | 0h  |

| Proces     | sors  |     |

| Publication | # 41322    | Revision: | 3.92 |  |

|-------------|------------|-----------|------|--|

| ssue Date:  | March 2012 |           |      |  |

Advanced Micro Devices 🗖

https://www.amd.com/system/files/TechDocs/41322\_10h\_

Occasionally, AMD identifies product errata that cause the processor to deviate from published specifications. Descriptions of identified product errata are designed to assist system and software designers in using the processors described in this revision guide. This revision guide may be updated periodically.

#### 298 L2 Eviction May Occur During Processor Operation To Set Accessed or Dirty Bit

#### Description

The processor operation to change the accessed or dirty bits of a page translation table entry in the L2 from 0b to 1b may not be atomic. A small window of time exists where other cached operations may cause the stale page translation table entry to be installed in the L3 before the modified copy is returned to the L2.

In addition, if a probe for this cache line occurs during this window of time, the processor may not set the accessed or dirty bit and may corrupt data for an unrelated cached operation.

#### **Potential Effect on System**

One or more of the following events may occur:

- Machine check for an L3 protocol error. The MC4 status register (MSR0000\_0410) is B2000000\_000B0C0Fh or BA000000\_000B0C0Fh. The MC4 address register (MSR0000\_0412) is 26h.

- · Loss of coherency on a cache line containing a page translation table entry.

- Data corruption.

#### Suggested Workaround

BIOS should set MSRC001\_0015[3] (HWCR[TlbCacheDis]) to 1b and MSRC001\_1023[1] to 1b. 4

In a multiprocessor platform, the workaround above should be applied to all processors regardless of

#### **Errata Statistics**

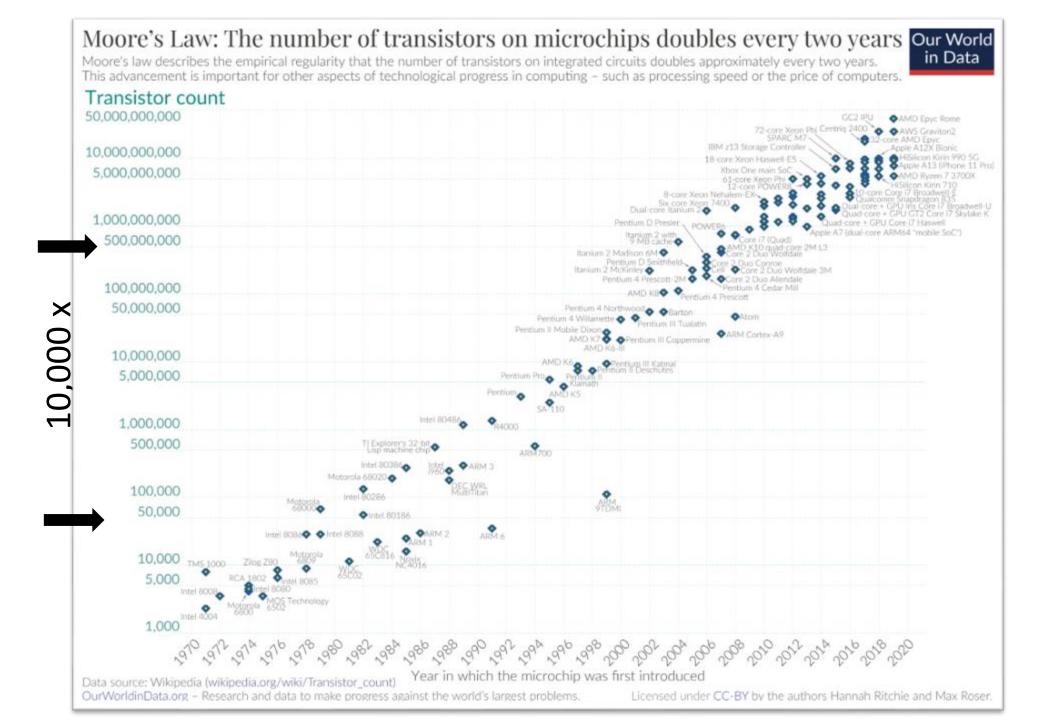

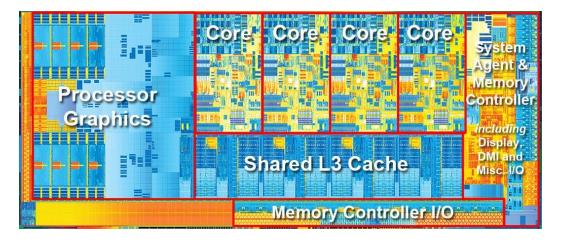

The Core-i7 processor with integrated graphics card in 2012 with 1,400M Transistors

#### 4 years; 136 errata; 3 bugs/month

SPECS: A Lightweight Runtime Mechanism for Protecting Software from Security-Critical Processor Bugs; Hicks et al; ASPLOS'15 https://github.com/impedimentToProgress/specs A **4-fold increase** in bugs in Intel processor designs **per generation**. Approximately 8000 bugs designed into the Pentium 4 ('Willamette')

from https://www.cl.cam.ac.uk/~jrh13/slides/nijmegen-21jun02/slides.pdf

## Outline

- Hardware Bug Examples

- How do they look like? The discovery process? Impact?

- #1: The famous Pentium FDIV bug

- #2: SYSRET 64-bit OS privilege escalation vulnerability on Intel CPU

- #3: Branch history injection attack

- How to discover hardware bugs?

- Manual efforts, testing

- Fuzzing

- Formal verification (next lecture)

### **Bug #1: Pentium FDIV Bug**

- What is the specification for floating-point computation?

- Floating is encoded as  $(1 + f) \times 2^e$ ,  $0 \le f < 1, e \in Z$

- Example:  $1/10 = 1.9999 \dots 9a \times 2^{-4}$  (in hexadecimal)

- We always have errors when doing floating-point computation, because we have limited number of bits for each floating number

- The specification allows error to occur after bit  $\boldsymbol{x}$

|                   | Single<br>precision                 | Double<br>precision                  | Extended precision                    |

|-------------------|-------------------------------------|--------------------------------------|---------------------------------------|

| Word size in bits | 32                                  | 64                                   | 80                                    |

| Bits for <i>f</i> | 23                                  | 52                                   | 63                                    |

| Bits for <i>e</i> | 8                                   | 11                                   | 15                                    |

| Relative accuracy | $2^{-23} \approx 1.2 \cdot 10^{-7}$ | $2^{-52} \approx 2.2 \cdot 10^{-16}$ | $2^{-63} \approx 1.1 \cdot 10^{-19}$  |

| Approximate range | $2^{\pm 127} \approx 10^{\pm 38}$   | $2^{\pm 1023} \approx 10^{\pm 308}$  | $2^{\pm 16383} \approx 10^{\pm 4964}$ |

The Pentium FDIV bug: see errors much earlier than the expected x bits

The computational aspects of the Pentium affairs. Coe et al. IEEE 1995 https://people.cs.vt.edu/~naren/Courses/CS3414/assignments/pentium.pdf

# The Discovery Process #1: Nicely's Prime

- Thomas Nicely, a mathematics professor, tried to compute reciprocal of prime numbers: p = 824, 633, 702, 441

- The correct result:

$1/p = 1.212659629408667 \times 10^{-12}$

Differ after the 9th digit

But the new Pentium processor gives:

$1/p = 1.212659624891158 \times 10^{-12}$

Took him four months to confirm the problem was NOT in his program -> math libraries -> compilers -> operating system, but in the hardware

### The Discovery Process #2: Kaiser's List

- Andreas Kaiser, a computer consultant

- Generate 25 *billion* random integers and checked the accuracy of the computed reciprocals. 23 are incorrect.

| 8  | 3221224323   | =  | 1.7ffff70600000 | , | 231             |

|----|--------------|----|-----------------|---|-----------------|

|    | 12884897291  | =  | 1.7ffff70580000 | • | 233             |

|    | 206158356633 | =  | 1.7ffff704c8000 |   | 237             |

|    | 824633702441 | =  | 1.7fffff7052000 | • | 2 <sup>39</sup> |

| 1  | 443107810341 | ÷  | 1.4fffedac25000 |   | 240             |

| 6  | 597069619549 | =  | 1.7fffff7057400 |   | 242             |

| 9  | 895574626641 | 12 | 1.1fffc6bc2a200 |   | 243             |

| 13 | 194134824767 | =  | 1.7ffff704e7e00 |   | 243             |

| 26 | 388269649885 | =  | 1.7ffff704fdd00 | • | 244             |

| 52 | 776539295213 | =  | 1.7ffff7046f680 |   | 2 <sup>45</sup> |

|    |              |    |                 |   |                 |

Patterns?

- Many are started with 1.7*fff*

- In another word, the first 20 bits after the leading bit have to be a single zero, followed by at least 19 ones

Pentium computed the reciprocals of these numbers inaccurately

#### The Discovery Process #3: Coe's Ratio

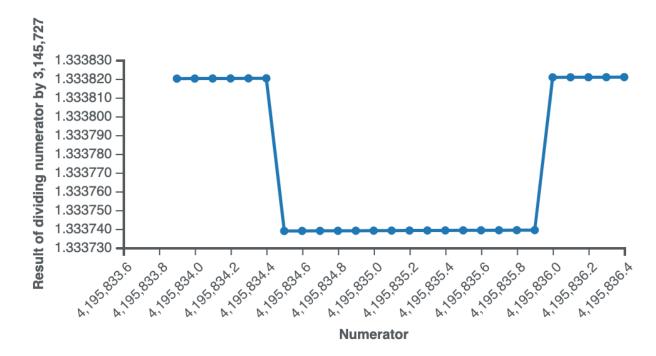

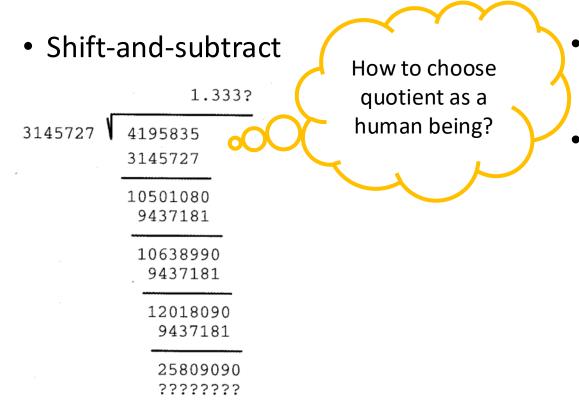

• Tim Coe, electrical engineer, has designed floating-point chips •  $\frac{4,195,835}{3,145,727} = 1.33382044 \dots$  (correct) 1.33373906... (Pentium)

The erorrs involve y/x where x and y's bit patterns conspire to excite the bug at an early stage in the division.

Differ after

the 4th digit

## **Bug Explanation: FDIV**

A combination of trial and error, experience, pattern matching and luck.

- Old processors: choose quotient from 0, 1

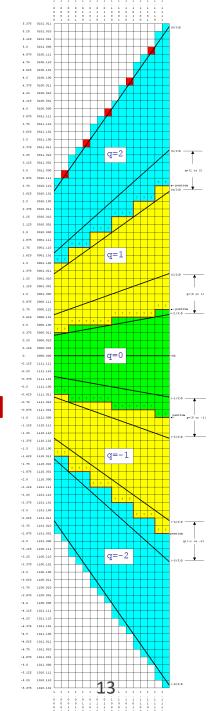

- Faster <u>Sweeney, Robertson, and Tocher</u> (SRT) algorithm Radix-4:

- Choose quotient from 0, +1, -1, +2, -2;

- If the current quotient is incorrectly chosen, we can recover it from the next iteration

- Guess the quotient based on the first few digits => use a 2D table to lookup

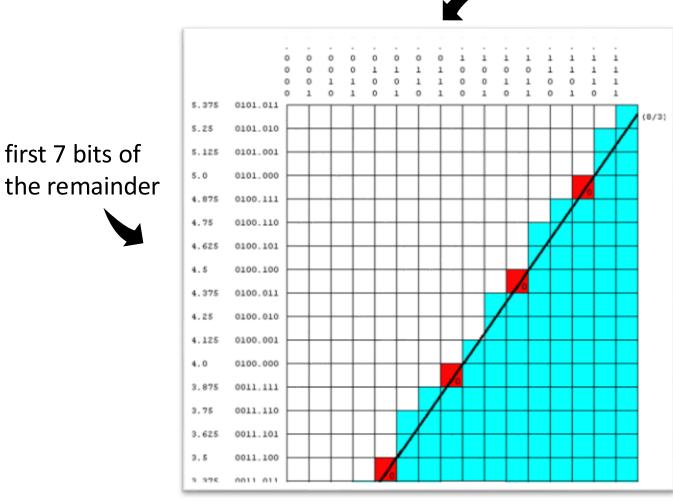

# **Bug Explanation: SRT Table**

first 5 bits of the divisor

- 2048 cells in total

- 1066 cells in use

- 5 cells are not initialized

- When the bug will be triggered?

# How Frequently the bug can be triggered?

- Intel: an average spreadsheet user could encounter this flaw once in every 27,000 years, assuming 1,000 divisions per day.

- IBM: suspended sales of Pentium-based models and said it is as many as 20 mistakes per day.

- Who actually got affected?

- Normal users?

- Wall street? Financial pre-diction programs? Did the Pentium bug flip a trading decision from buy to hold to sell?

- Difficult to calibrate

# **Consequences/Impacts**

- Intel's bad responses

- Conditional replacement (customers need to claim they do get influenced by the bug) → disastrous press

- No-questions-asked replacement → \$475M cost in 1994, 10% replacements

- Potential long-term impact:

- Random test is not be a good idea. Exhaustive test has scalability problem.

- A marked increase in the use of formal verification and number theory in hardware design

#### Some humor for you: Q: How many Pentium designers does it take to screw in a light bulb? A: 1.99904274017, but that's close enough for non-technical people. Q: What do you get when you cross a Pentium PC with a research grant? A: A mad scientist. Do you think it bothers x86 users that the 486 is a functional upgrade to the Pentium? In response to the Pentium bug, PowerMac officials have announced that they will be adding the control panel "Pentium Switcher" that allows users to decide whether the PowerMac should emulate pre-Pentium or post-Pentium FDIV behaviour. TOP TEN NEW INTEL SLOGANS FOR THE PENTIUM 9.9999973251 It's a FLAW, Dammit, not a Bug 8.9999163362 It's Close Enough, We Say So 7.9999414610 Nearly 300 Correct Opcodes 6.9999831538 You Don't Need to Know What's Inside 5.9999835137 Redefining the PC--and Mathematics As Well 4.9999999021 We Fixed It, Really

3.9998245917 Division Considered Harmful 2.9991523619 Why Do You Think They Call It \*Floating\* Point? 1.9999103517 We're Looking for a Few Good Flaws 0.9999999998 The Errata Inside

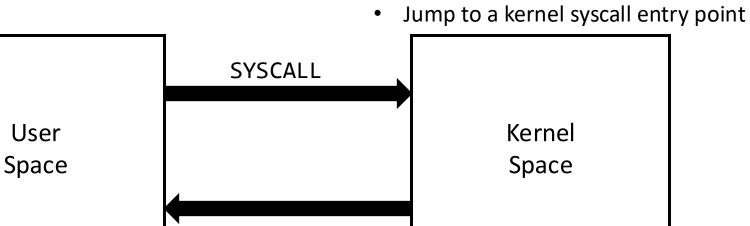

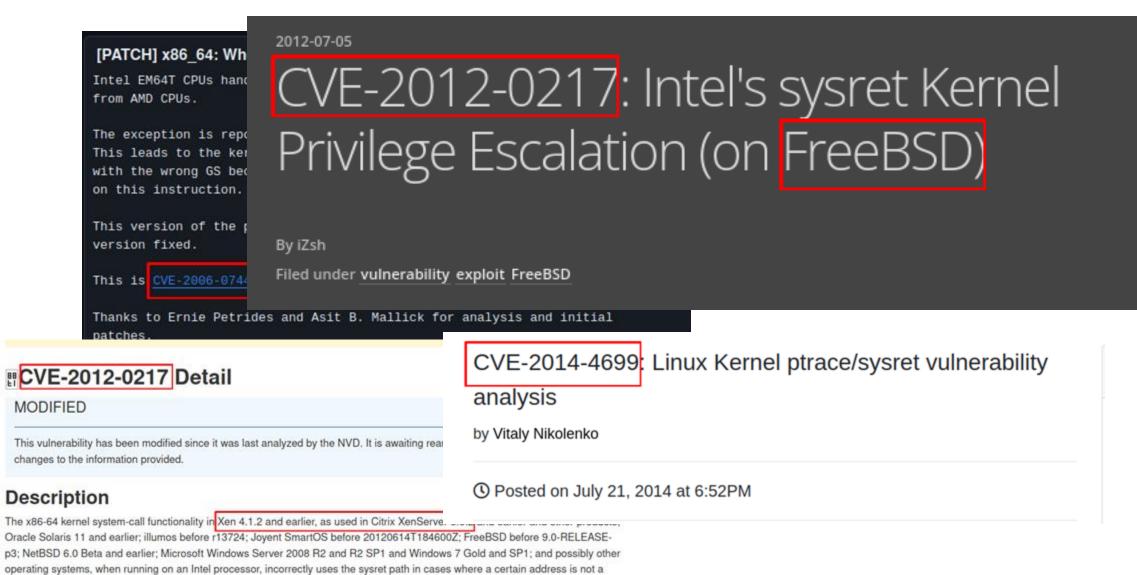

### Bug #2: A SYSRET Bug

64-bit x86 instruction set: AMD64, Intel 64

SYSCALL

- HW transits from user mode to kernel mode

- Save the userspace next-PC to the RCX register

HW transits from kernel mode to user mode

Restore the userspace next-PC from the RCX register

SYSRET

A Stitch In Time Saves Nine: A Stitch In Time Saves Nine: A Case Of Multiple OS Vulnerability; Rafal Wojtczuk; BlackHat, 2012

Model Checking to Find Vulnerabilities in an Instruction Set Architecture; Bradfield et al; HOST'16

SYSRET

16

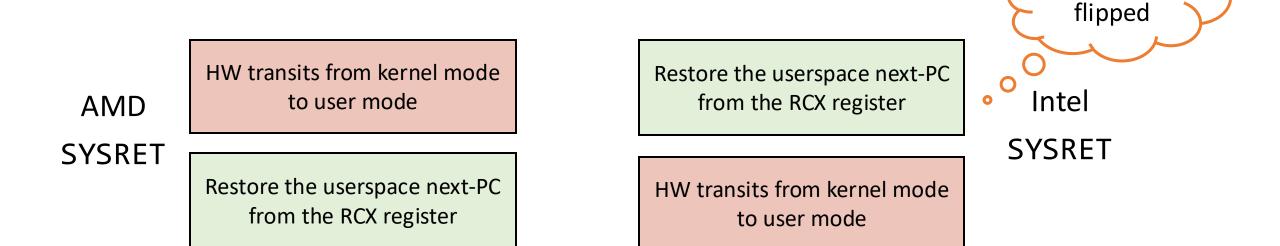

#### **Two Different Specifications for SYSRET**

Order is

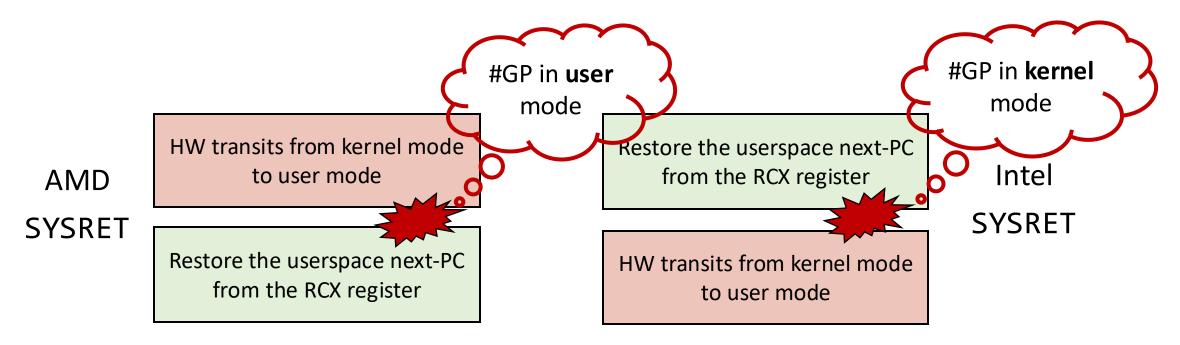

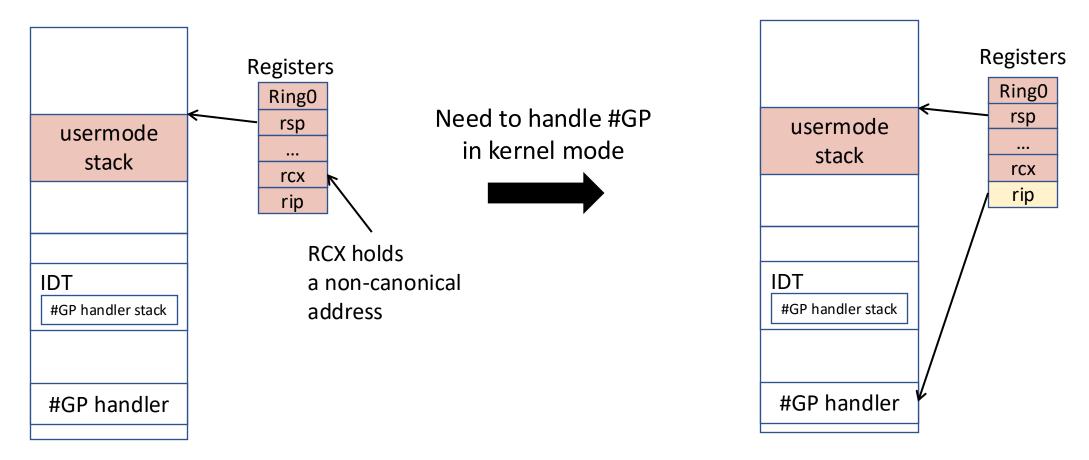

### **SYSRET Vulnerability**

If RCX holds a non-canonical address, the SYSRET will generates a #GP (general protection fault) Canonical means that given 48-bit virtual address space, the high 16 bits (bits 63-48) of a virtual address have same value as bit 47.

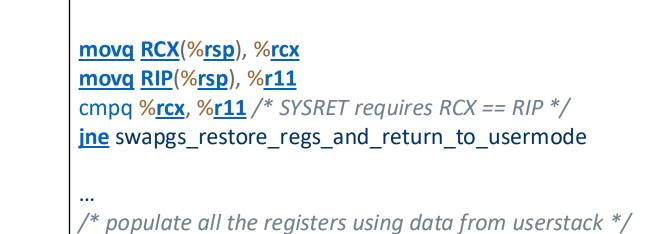

### How SYSRET is used in kernel code?

• What do we do before we transition from kernelspace to userspace?

At this point, all the registers are user-controlled (attacker-controlled)

sysret

https://elixir.bootlin.com/linux/latest/source/arch/x86/entry/entry\_64.S

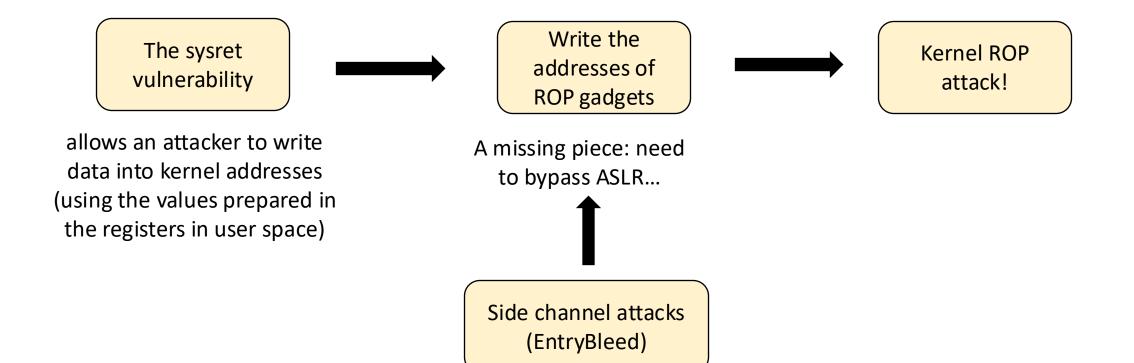

#### **SYSRET Attack on Intel Processors**

Before executing SYSRET, all registers have been restored using usermode context

Assume rip points to kernel stack and start using it --> can **overwrite kernel data**

#### Longtime Intel x86 OS Bug

21

### **Exploiting Sysret on Linux in 2023**

# It's not a bug, it's a feature

#### Description

SYSRET is a compan code at privilege leve size, SYSRET remain ters are loaded.

```

Operation

IF (CS.L \neq 1) or (IA32_EFER.LMA \neq 1) or (IA32_EFER.SCE \neq 1)

(* Not in 64-Bit Mode or SYSCALL/SYSRET not enabled in IA32_EFER *)

THEN #UD; FI;

IF (CPL \neq 0) THEN #GP(0); FI;

IF (operand size is 64-bit)

THEN (* Return to 64-Bit Mode *)

IF (RCX is not canonical) THEN #GP(0);

RIP := RCX:

ELSE (* Return to Compatibility Mode *)

RIP := ECX:

FI;

(* Clear RF, VM, reserved bits; set bit 1 *)

RFLAGS := (R11 & 3C7FD7H) | 2;

IF (operand size is 64-bit)

THEN CS.Selector := IA32_STAR[63:48]+16;

ELSE CS.Selector := IA32_STAR[63:48];

(* RPL forced to 3 *)

CS.Selector := CS.Selector OR 3;

(* Set rest of CS to a fixed value *)

CS.Base := 0;

(* Flat segment *)

CS.Limit := FFFFFH;

(* With 4-KByte granularity, implies a 4-GByte limit *)

(* Execute/read code, accessed *)

CS.Type := 11;

CS.S := 1;

CS.DPL := 3;

CS.P := 1;

IF (operand size is 64-bit)

THEN (* Return to 64-Bit Mode *)

```

OS system-call handler to user om R11.<sup>1</sup> With a 64-bit operand only the low 32 bits of the regis-

#### It's not a bug, it's a feature

Intel claims that this vulnerability is a software implementation issue, as their processors are functioning as per their documented specifications. However, software that fails to take the Intel-specific SYSRET behavior into account may be vulnerable.

https://www.kb.cert.org/vuls/id/649219

### Who to blame?

- Intel claims it is not an errata

- Errata are design defects or errors that may cause ... behavior to deviate from published specifications.

- This behavior is consistent with Intel's specification

- So the problem is the specification is incorrect

- Intel SDM (software development manual) 3400 pages. We cannot assume the specification is always correct.

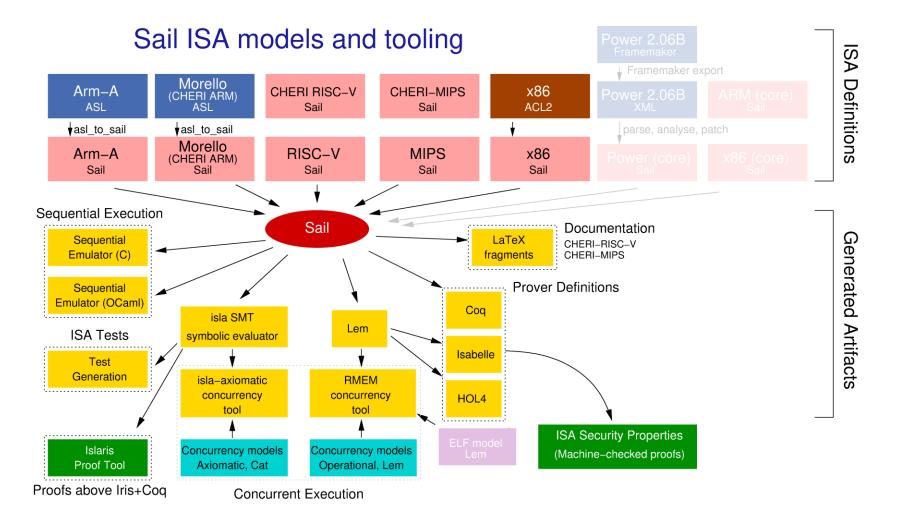

- Research question: how can we know the ISA specification is correct?

- Some research efforts to verify ISA specification

### The Sail ISA specification language

https://github.com/rems-project/sail

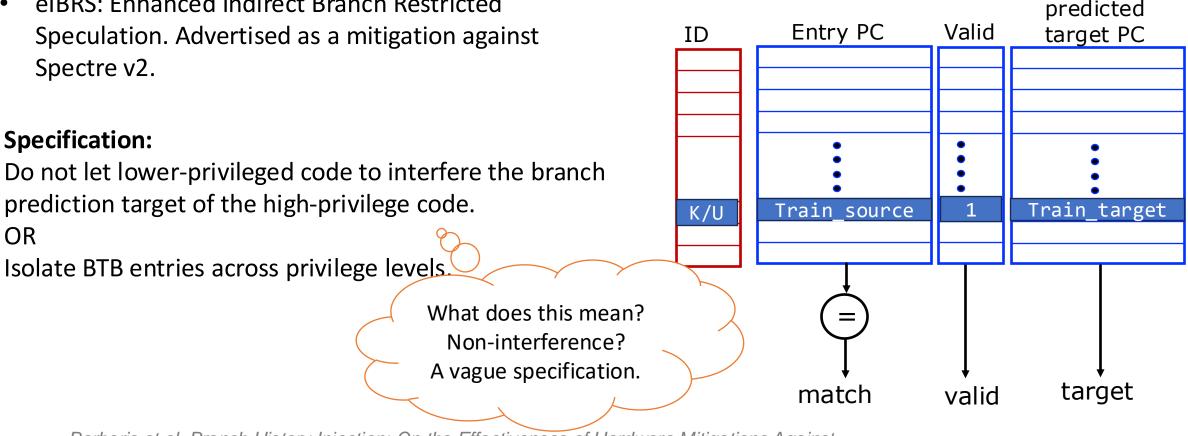

# **Bug #3: elBRS Vulnerability**

- Recap Spectre v2

- elBRS: Enhanced Indirect Branch Restricted Speculation. Advertised as a mitigation against Spectre v2.

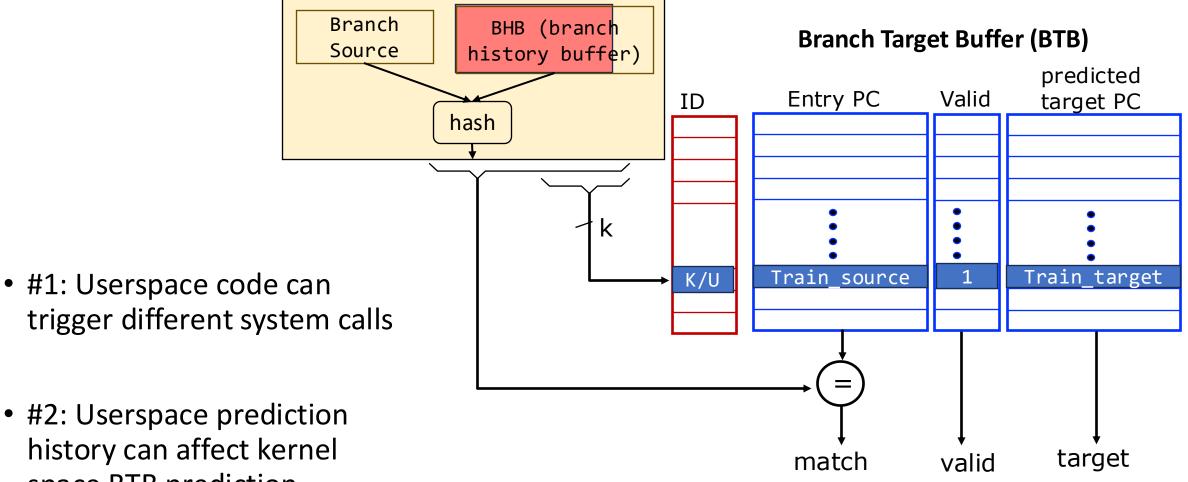

#### **Branch Target Buffer (BTB)**

Barberis et al. Branch History Injection: On the Effectiveness of Hardware Mitigations Against Cross-Privilege Spectre-v2 Attacks. USENIX'22 https://www.vusec.net/projects/bhi-spectre-bhb/

#### **Recap the Problem: Branch History Injection**

• #2: Userspace prediction history can affect kernel space BTB prediction

Bugs in the specification

Vague specification

- Next: How to find hardware bugs?

- Get ideas from the software

# **Software Bugs Hunting/Fixing**

- Approach 1: Manual effort

- Hire a lot of experts and stare at the code

- Regression test  $\rightarrow$  but need to be updated

- Approach 2: How about randomly generating test cases?

- Fuzzing

- Approach 3: Formal verification

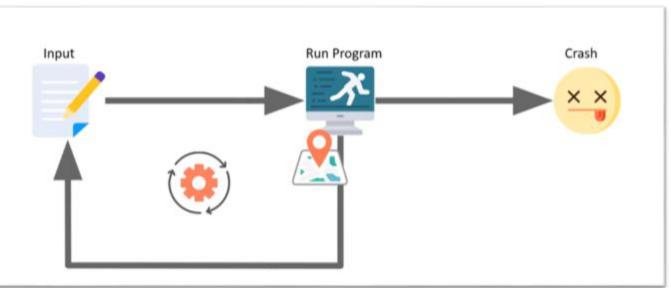

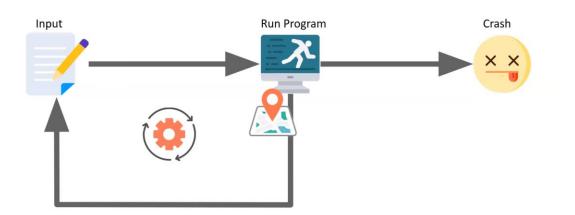

# Fuzzing

### **Fuzzing In A Nutshell**

- Automatic generate test examples

- 1999, Alan Cox at University of Wales discovered a vulnerability in Linux kernel by simply running a proram generating random input and feed into the kernel

- Crash is generated by assertions/specifications

- Simple yet effective

- Industry standard for software

# **Fuzzing Components**

- Random seeds

- Sometimes need formatted inputs, e.g., PDF reader

- A criteria to check whether the outcome is as expected or not.

- Specification

- Security invariant (paper discussion SPECS)

- Assertions (address sanitizer)

- Heuristics for generating new tests => feedback loop for better efficiency

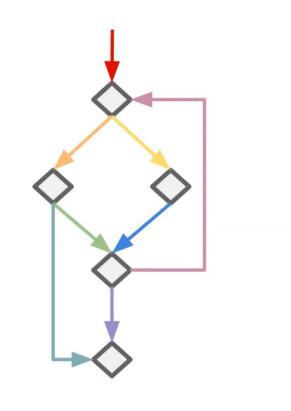

# **Types of Fuzzing**

- Blackbox

- Greybox

- Whitebox

| Co | lecte | ed co | over | age: |   |   |   |

|----|-------|-------|------|------|---|---|---|

| 1  | 6     | 2     | 6    | 0    | 2 | 1 | 7 |

From Blackbox Fuzzing to Whitebox Fuzzing towards Verification; Patrice Godefroid; Microsoft Research

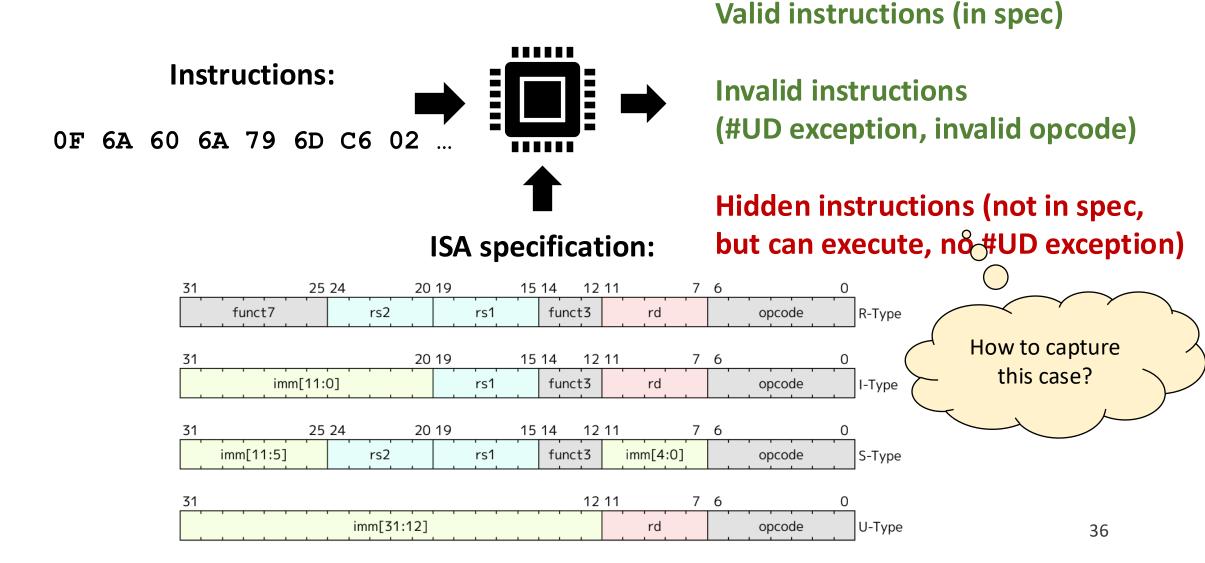

### **Example: Hidden Instructions**

• There exist holes in instruction encoding:

| 31                                                   | 25 24                                             | 20 19                             | 15 14 12 11                                         | 7 6                               | 0                         |

|------------------------------------------------------|---------------------------------------------------|-----------------------------------|-----------------------------------------------------|-----------------------------------|---------------------------|

| funct7                                               | rs2                                               | rs1                               | funct3                                              | rd                                | opcode                    |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | 5<br>0 0 src2<br>0 0 src2<br>0 0 src2<br>0 0 src2 | 5<br>src1<br>src1<br>src1<br>src1 | 3<br>ADD/SLT[U]<br>AND/OR/XOR<br>SLL/SRL<br>SUB/SRA | 5<br>dest<br>dest<br>dest<br>dest | 7<br>OP<br>OP<br>OP<br>OP |

*The RISC-V Instruction Set Manual Volume I: Unprivileged ISA*

- Hidden instructions: secret instructions that give backdoor or powerful access to processor internals

- Secret processor functionality: Appendix H

- An example:

- Pentium FOOF bug, an invalid instruction freezes the cpu, discovered in 1997

- A Ring 3 process can DOS (denial of service) a process

- The invalid instruction encoding is: **F0 OF C7 [C8-CF]**

#### **Search for Hidden Instructions**

### **More Hardware Fuzzing Examples**

• Zenbleed: found a CPU bug via post-silicon fuzzing

| movnti [rbp+0x0],ebx                       | movnti [rbp+0x0],ebx                                                                    |

|--------------------------------------------|-----------------------------------------------------------------------------------------|

|                                            | sfence                                                                                  |

| rcr dh,1                                   | rcr dh,1                                                                                |

|                                            | lfence                                                                                  |

| sub r10, rax                               | sub r10, rax                                                                            |

|                                            | mfence                                                                                  |

| rol rbx, cl                                | rol rbx, cl                                                                             |

|                                            | nop                                                                                     |

| <pre>xor edi,[rbp-0x57]</pre>              | xor edi,[rbp-0x57]                                                                      |

| A randomly generated sequence of instructi | ons, and the same sequence but with randomized alignment, and speculation fences added. |

37

### Summary

- Hardware bugs

- Deviate from specification (errata)

- Incorrect and vague specification

- Potential approaches to find hardware bugs

- Manual analysis, testing

- Fuzzing

- Formal Verification (next lecture)

Program testing can be quite effective for showing the presence of bugs, but is hopelessly inadequate for showing their absence. – Edsger Dijkstra